Architecture and working principle of arm single chip microcomputer

Arm single chip microcomputer (advance risk machine), which is one of the most widely used and licensed processor cores in the world. The first arm processor was developed by Cambridge University in 1978, and the first arm RISC processor was produced by acorn group of computers in 1985. These processors are designed for portable devices, such as digital cameras, mobile phones, home networks. Due to the advantages such as low power consumption and reasonable performance, these modules and wireless communication technology and other embedded systems can also be used. This paper summarizes the arm architecture and the working principle of each module.

Arm architecture

Arm architecture processor is an advanced reduced instruction set computing (RISC) machine and a 32-bit reduced instruction set computer (RISC) single chip microcomputer. It was launched by acron computer organization in 1987. The arm is a single chip microcomputer series developed by St microelectronics, Motorola and other manufacturers. Arm architecture has completely different versions, such as armv1, armv2, etc., and each version has its own advantages and disadvantages.

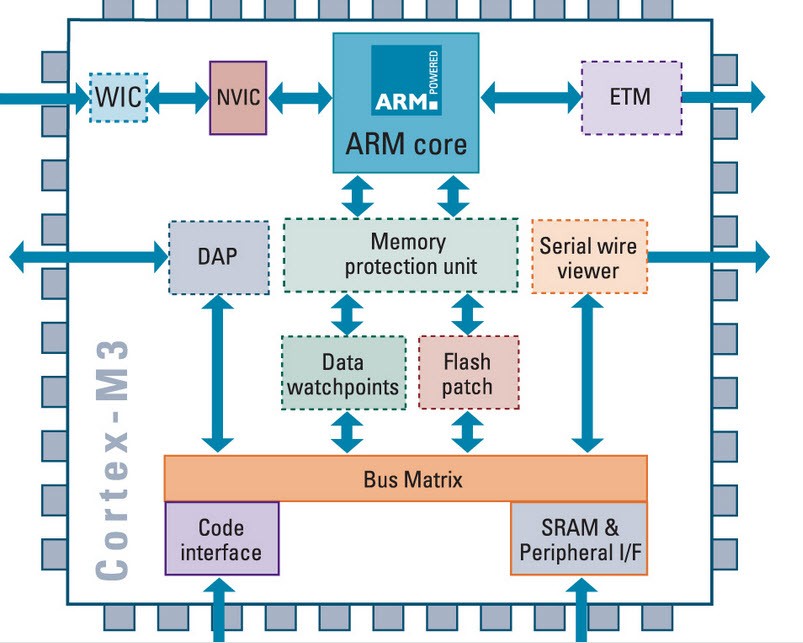

Arm cortex is a complex single chip microcomputer with armv7 design in arm series. There are three sub Series in the arm cortex series:

Arm cortex ax series;

Arm cortex RX series;

Arm cortex MX series.

Arm architecture

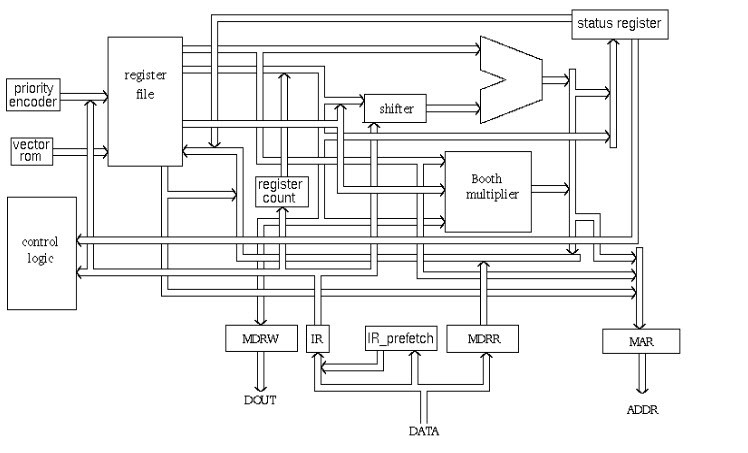

1. Arithmetic logic unit;

2. Booth multiplier;

3. Barrel shifter;

4. Control unit.

In this paper, the single chip microcomputer scheme network introduces each component of arm.

ARM processors also have other components, such as program status registers, which contain processor flags (Z, s, V, and C). In addition to the interrupt and fast interrupt inhibit bits, the mode bits also exist in the routine register of the program. Some special registers: some registers are used for instructions, memory data read-write registers and memory address registers.

Priority encoder: the encoder is used in multiple load and store instructions to indicate which register in the register file to load or retain.

Multiplexers: Several multiplexers are used to the management operation of the processor bus. Due to the limited project time, we prefer to implement these components in the behavior model. Each component has an entity description. Each entity has its own architecture, which can be optimized for some needs according to its application. This makes the design easier to build and maintain.

Arithmetic logic unit (ALU)

Alu has two 32-bit inputs. The main variable comes from the register file and the other variable comes from the shifter. The status register flag is modified by the ALU output. The v-bit output goes to the V flag and the count goes to the C flag. Although the most significant bit actually represents the s flag, the ALU output operation is completed by nored to obtain the Z flag. Alu has 4-bit function bus and can realize up to 16 operation codes.

multiplication factor

The multiplier factor has three 32-bit inputs that are returned from the register file. The multiplier output is only the 32 least significant bits of the commodity. The figure above shows the entity representation of the multiplier factor. Multiplication starts whenever the 04 input is activated. After completion, the output fin becomes high.

Booth algorithm

Booth algorithm is a noteworthy multiplication algorithm rule of 2 complement. In this way, positive and negative numbers can be treated uniformly. In addition, without performing any addition or subtraction, the trip of 0 or 1 within the multiplier factor is skipped, so that faster multiplication may be achieved. This figure shows the simulation results of multiplier test bench. Obviously, the multiplication is completed in only 16 clock cycles.

Barrel shifter

The barrel shifter has a 32-bit input to shift. This input is returned from a register file, or it may be immediate data. The shifter has different control inputs returned from the instruction register. The shift field in the command controls the operation of the barrel shifter. This field indicates the type of shift to perform (logical left or right, arithmetic right or right rotation). The number of registers that should be shifted is contained in the immediate number field of the instruction, or may be the lower 6 bits of the register in the register file.

shift_ The Val input bus is 6 bits, and 32-bit shift is allowed at most. The shift type indicates the required shift types 00, 01, 10 and 11 corresponding to left shift, right shift, arithmetic right shift and right rotation, respectively. Barrel shifters are especially created by multiplexers.

control unit

For any microprocessor, the control unit is the core of the whole process. It is responsible for the operation of the system. Therefore, the design of the control unit is the most important part of the whole design. The control unit is sometimes a pure combinational circuit design. Here, the control unit is realized by a simple state machine. The processor timing is additionally included in the control unit. Signals from the control unit are connected to each component in the processor to supervise its operation.

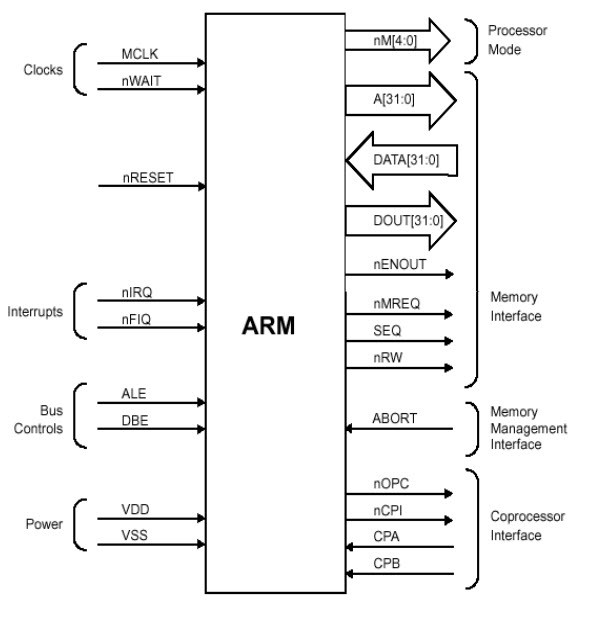

Function diagram of arm single chip microcomputer

The last thing that must be explained is the use of arm and the display of the chip. Various signals interfaced with the processor are input, output or monitoring signals, which will be used to control arm operation.

Other uses of cortex processor

1. It is the computing controller of reduced instruction set

32-bit high-performance CPU;

Three stage pipe, compact.

2. It has thumb-2 technology

Combined with 16 / 32-bit instructions;

High performance.

3. It supports tools and RTOS and its core sight debugging and tracking

JTAG or 2-pin serial line debugging connection;

Multiple processors are supported.

4. Low power consumption mode

It supports sleep mode;

Control software package;

Multiple power domains.

5. Nested vector interrupt controller (NVIC)

Low delay, low noise interrupt response;

No assembly programming is required.